# hyperCache™ / Stand-Alone PCI Peripheral Controller with USB

#### **Features**

- PCI to ISA bridge

- PCI Bus Rev. 2.1 compliant

- Supports up to 5 additional PCI masters including the CY82C691

- Integrated DMA controllers with Type A, B, and F support

- Integrated Interrupt controllers

- · Integrated timer/counters

- Integrated Real-Time-Clock with 256 bytes of battery-backed SRAM (14 bytes of clock RAM and 242 bytes of CMOS scratch RAM)

- Write-only Register Shadowing

- Integrated Dual-Channel enhanced IDE controller with

- PCI bus mastering

- -CD ROM support

- PIO modes 0 through 4 operation

- Single-word and Multi-word DMA modes 0 through 2

- Integrated Keyboard Controller

- APM compliant power management support through SMM or under hardware control

- Flash PROM support with write-protection

- · Power-on reset circuitry

- QuietBus™ support for the PCI and ISA bus interfaces for better noise immunity

- · General-purpose I/O pins and registers

- USB Host/Hub controller with 2 USB ports

- Flexible Stand-Alone configuration options

- Packaged in a 208-pin PQFP

hyperCache and QuietBus are trademarks of Cypress Semiconductor Corporation. Pentium is a trademark of Intel Corporation.

# **TABLE OF CONTENTS**

| Features                                                        |    |

|-----------------------------------------------------------------|----|

| CY82C693UB Signals                                              | 11 |

| Pin Configuration                                               |    |

| CY82C693UB Pin Reference (In Numerical Order by Pin Number)     |    |

| CY82C693UB Pin Reference (In Alphabetical Order by Signal Name) |    |

| Introduction                                                    |    |

| System Overview                                                 |    |

| CY82C693UB Introduction                                         |    |

|                                                                 |    |

| Functional Overview                                             |    |

| PCI Bus Interface                                               |    |

| ISA Bus Interface                                               |    |

| Reset Logic                                                     |    |

| Keyboard Controller                                             |    |

| Operating Frequency                                             |    |

| Resetting the Keyboard Controller  Host Interface               |    |

| PS/2 Compatible Mouse Support                                   |    |

| Keyboard Interface                                              |    |

| Maximum Flexibility                                             |    |

| Keyboard Self-Test                                              |    |

| Power Management Logic                                          |    |

| AT Refresh Logic                                                |    |

| Pre-Read/Post-Write Buffers                                     |    |

| BIOS ROM Control                                                |    |

| Timer/Counter Logic                                             | 20 |

| DMA Controllers                                                 |    |

| DMA Controller Transfer Modes                                   |    |

| IDE Controller                                                  | 21 |

| Real-Time-Clock                                                 | 21 |

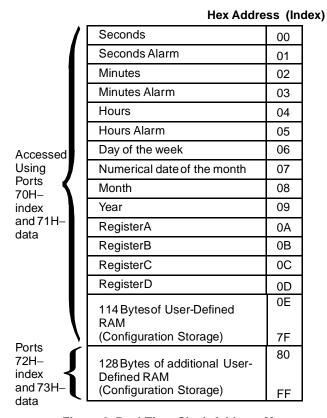

| RTC Address Map                                                 | 22 |

| External RTC Control                                            |    |

| Interrupt Controllers                                           |    |

| NMI Sources                                                     |    |

| Stand-Alone Operation                                           |    |

| Use With An External PCI Arbiter                                |    |

| Splitting GNTBSY                                                |    |

| External Reset Control                                          |    |

| FREQACK Bypassing                                               |    |

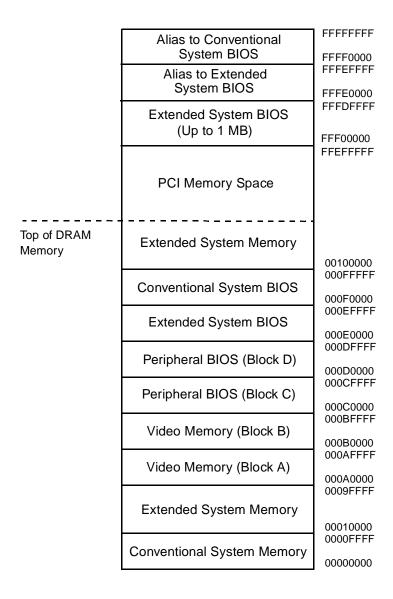

| 1 Mbyte ROM Decode                                              |    |

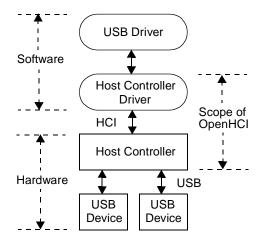

| Universal Serial Bus (USB) Host Controller                      |    |

| CY82C693UB Signal Description                                   |    |

| Reset Signals                                                   |    |

| PCI Interface Signals                                           |    |

| ISA Interface Signals                                           |    |

| Power Management Signals                                        |    |

|                                                                 |    |

| Keyboard Interface SignalsIDE Interface Signals                 |    |

| USB Interface Signals                                           |    |

| Miscellaneous Signals                                           |    |

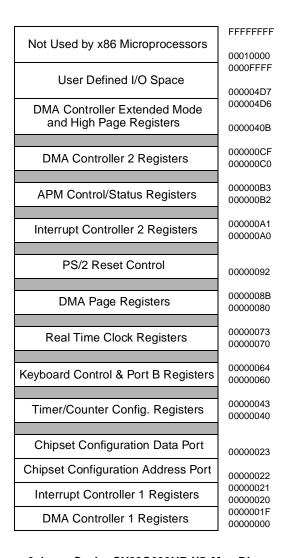

| hyperCache Memory and I/O Map                                   |    |

|                                                                 |    |

| CY82C693UB Control Registers                                    |    |

| Register 1: Peripheral Configuration Register #1 (Read/Write) — Index=01H                   | 37 |

|---------------------------------------------------------------------------------------------|----|

| Register 2: Peripheral Configuration Register #2 (Read/Write) - Index=02H                   |    |

| Register 3: Interrupt Request Level/Edge Control Register #1 (Read/Write) - Index=03H       | 38 |

| Register 4: Interrupt Request Level/Edge Control Register #2 (Read/Write) - Index=04H       | 39 |

| Register 5: Real-Time-Clock Configuration Register (Read/Write) - Index=05H                 | 39 |

| Write-Only Shadow Registers                                                                 | 40 |

| Register 80: DMA1 Write Request Shadow Register (Read/Write) - Index=80H                    | 40 |

| Register 81: DMA1 Write Single Mask Bit Shadow Register (Read/Write) - Index=81H            | 40 |

| Register 82: DMA1 Write Mode Shadow Register (Read/Write) - Index=82H                       |    |

| Register 83: DMA1 Clear Byte Pointer Shadow Register (Read/Write) - Index=83H               | 40 |

| Register 84: DMA1 Master Clear Shadow Register (Read/Write) - Index=84H                     | 40 |

| Register 85: DMA1 Clear Mask Shadow Register (Read/Write) - Index=85H                       | 40 |

| Register 86: Timer Counter 1 Command Mode Shadow Register (Read/Write) - Index=86H          | 40 |

| Register 87: CMOS Battery-Backed RAM Address and NMI Mask Registers Shadow Register         |    |

| (Read/Write) - Index=87H                                                                    | 40 |

| Register 88: DMA2 Write Request Shadow Register (Read/Write) - Index=88H                    |    |

| Register 89: DMA2 Write Single Mask Bit Shadow Register (Read/Write) - Index=89H            | 41 |

| Register 8A: DMA2 Write Mode Shadow Register (Read/Write) - Index=8AH                       |    |

| Register 8B: DMA2 Clear Byte Pointer Shadow Register (Read/Write) - Index=8BH               |    |

| Register 8C: DMA2 Mask Clear Shadow Register (Read/Write) - Index=8CH                       |    |

| Register 8D: DMA2 Clear Mask Shadow Register (Read/Write) - Index=8DH                       |    |

| Register 8E: Coprocessor Error Shadow Register (Read/Write) - Index=8EH                     |    |

| Register 8F: Extended CMOS RAM address Shadow Register (Read/Write) - Index=8FH             |    |

| General Purpose I/O Registers                                                               |    |

| Register 90: General Purpose I/O Control Register A (Read/Write) - Index=90H                |    |

| Register 91: General Purpose I/O Input/Output Control Register A (Read/Write) - Index=91H   |    |

| Register 92: General Purpose I/O Control Register B (Read/Write) - Index=92H                |    |

| Register 93: General Purpose I/O Input/Output Control Register B (Read/Write) - Index=93H   |    |

| Power Management Control Registers                                                          |    |

| Register 40: Standby Timer Event Detection Control (Read/Write) - Index=40H                 |    |

| Register 41: Standby Timer Interrupt Request Detection Control #1 (Read/Write) - Index=41H  |    |

| Register 42: Standby Timer Interrupt Request Detection Control #2 (Read/Write) - Index=42H  |    |

| Register 43: Standby Timer DMA Request Detection Control #1 (Read/Write) - Index=43H        |    |

| Register 44: Suspend Timer Event Detection Control (Read/Write) - Index=44H                 |    |

| Register 45: Suspend Timer Interrupt Request Detection Control #1 (Read/Write) - Index=45H  |    |

| Register 46: Suspend Timer Interrupt Request Detection Control #2 (Read/Write) - Index=46H  |    |

| Register 47: Suspend Timer DMA Request Detection Control #1 (Read/Write) - Index=47H        |    |

| Register 48: User Timer 1 Event Detection Control (Read/Write) - Index=48H                  |    |

| Register 49: User Timer 1 Interrupt Request Detection Control #1 (Read/Write) - Index=49H   |    |

| Register 4A: User Timer 1 Interrupt Request Detection Control #2 (Read/Write) - Index=4AH   |    |

| Register 4B: User Timer 1 DMA Request Detection Control #1 (Read/Write) - Index=4BH         |    |

| Register 4C: Throttle Timer Event Detection Control (Read/Write) - Index=4CH                |    |

| Register 4D: Throttle Timer Interrupt Request Detection Control #1 (Read/Write) - Index=4DH |    |

| Register 4E: Throttle Timer Interrupt Request Detection Control #2 (Read/Write) - Index=4EH |    |

| Register 4F: Throttle Timer DMA Request Detection Control #1 (Read/Write) - Index=4FH       | 52 |

| Register 50: Non-motherboard Memory Address Range Decode for Event Detection                |    |

| Register #1 (Read/Write) - Index=50H                                                        | 52 |

| Register 51: Non-motherboard Memory Address Range Decode for Event Detection                |    |

| Register #2 (Read/Write) - Index=51H                                                        | 52 |

| Register 52: Non-motherboard Memory Address Mask for Event Detection Register #1            |    |

| (Read/Write) - Index=52H                                                                    | 52 |

| (Decad Milita) Lindox COLL                                                                          |    |

|-----------------------------------------------------------------------------------------------------|----|

| (Read/Write) - Index=53H                                                                            | 52 |

| Register 54: Programmable I/O Trap 1 Address Range Register #1 (Read/Write) - Index=54H             | 52 |

| Register 55: Programmable I/O Trap 1 Address Range Register #2 (Read/Write) - Index=55H             | 53 |

| Register 56: Programmable I/O Trap 1 Address Range Register #3 (Read/Write) - Index=56H             | 53 |

| Register 57: Programmable I/O Trap 1 Address Range Register #4 (Read/Write) - Index=57H             | 53 |

| Register 58: Programmable I/O Trap 2 Address Range Register #1 (Read/Write) - Index=58H             | 53 |

| Register 59: Programmable I/O Trap 2 Address Range Register #2 (Read/Write) - Index=59H             | 53 |

| Register 5A: Programmable I/O Trap 2 Address Range Register #3 (Read/Write) - Index=5AH             |    |

| Register 5B: Programmable I/O Trap 2 Address Range Register #4 (Read/Write) - Index=5BH             |    |

| Register 5C: Programmable I/O Trap 1 Address Detection Control (Read/Write) - Index=5CH             |    |

| Register 5D: Programmable I/O Trap 2 Address Detection Control (Read/Write) - Index=5DH             | 54 |

| Register 5E: I/O Trap 1 and 2 Monitoring Control (Read/Write) - Index=5EH                           |    |

| Register 5F: Standby and Suspend Timer Terminal Count Control Register (Read/Write) - Index=5FH     |    |

| Register 60: User Timer 1 and User Timer 2 Terminal Count Control Register (Read/Write) - Index=60H |    |

| Register 61: User Timer 3 Terminal Count Control Register (Read/Write) - Index=61H                  |    |

| Register 62: Throttle Timer Terminal Count Control Register (Read/Write) - Index=62H                |    |

| Register 63: Power Management Control Register#1 (Read/Write) - Index=63H                           |    |

| Register 64: Power Management Control Register#2 (Read/Write) - Index=64H                           |    |

| Register 65: Power Management Clock Control Register (Read/Write) - Index=65H                       |    |

| Register 66: STOPCLK Control Register (Read/Write) - Index=66H                                      |    |

| Register 67: Power Management SMI Control Register (Read/Write) - Index=67H                         |    |

| Register 70: Power Management SMI Enable Register #1 (Read/Write) - Index=70H                       |    |

| Register 71: Power Management SMI Enable Register #2 (Read/Write) - Index=71H                       |    |

| Register 72: Power Management SMI Enable Register #3 (Read/Write) - Index=72H                       |    |

| Register 73: Power Management SMI Enable Register #4 (Read/Write) - Index=73H                       |    |

| Register 74: Power Management SMI Enable Register #5 (Read/Write) - Index=74H                       |    |

| Register 75: Power Management SMI Enable Register #6 (Read/Write) - Index=75H                       |    |

| Register 76: Power Management SMI Status Register #1 (Read/Write) - Index=76H                       |    |

| Register 77: Power Management SMI Status Register #2 (Read/Write) - Index=77H                       |    |

| Register 78: Power Management SMI Status Register #3 (Read/Write) - Index=78H                       |    |

| Register 79: Power Management Interrupt Request Status Register #1 (Read/Write) - Index=79H         |    |

| Register 7A: Power Management Interrupt Request Status Register #2 (Read/Write) - Index=7AH         |    |

| Register 7B: Power Management DMA Request Status Register (Read/Write) - Index=7BH                  | 68 |

| Register 7C: Reserved - Index=7CH                                                                   | 69 |

| Register 7D: Reserved - Index=7DH                                                                   | 69 |

| Register 7E: Reserved - Index=7EH                                                                   | 69 |

| Register 7F: Reserved - Index=7FH                                                                   | 69 |

| Special I/O Port Registers                                                                          | 70 |

| Port 61: System Control Port B, NMI (Read/Write) - I/O Address=061H                                 | 70 |

| Port 70: RTC/Configuration RAM Address Port, NMI (Write) - I/O Address=070H                         |    |

| Port 92: PS/2 Reset Control (Read/Write) - I/O Address=092H                                         | 70 |

| Port B2: APM Control Port (Read/Write) - I/O Address=0B2H                                           | 71 |

| Port B3: APM Status Port (Read/Write) - I/O Address=0B3H                                            | 71 |

| CY82C693UB DMA Controller Registers                                                                 | 72 |

| DMA Register 0: DMAC1 Channel 0 Current Address Register (Read/Write) - I/O Address=000H            |    |

| DMA Register 1: DMAC1 Channel 0 Current Word Count Register (Read/Write) - I/O Address=001H         |    |

| DMA Register 2: DMAC1 Channel 1 Current Address Register (Read/Write) - I/O Address=002H            |    |

| DMA Register 3: DMAC1 Channel 1 Current Word Count Register (Read/Write) - I/O Address=003H         |    |

| DMA Register 4: DMAC1 Channel 2 Current Address Register (Read/Write) - I/O Address=004H            |    |

| DMA Register 5: DMAC1 Channel 2 Current Word Count Register (Read/Write) - I/O Address=005H         |    |

| DMA Register 6: DMAC1 Channel 3 Current Address Register (Read/Write) - I/O Address=006H            |    |

| DMA Register 7: DMAC1 Channel 3 Current Word Count Register (Read/Write) - I/O Address=007H | 73  |

|---------------------------------------------------------------------------------------------|-----|

| DMA Register 8: DMAC1 Status/Command Register (Read/Write) - I/O Address=008H               | 73  |

| Status Register Format (Read Only)                                                          | 74  |

| Command Register Format (Write Only)                                                        | 75  |

| DMA Register 9: DMAC1 DMA Request Register (Write Only) - I/O Address=009H                  | 75  |

| DMA Request Register Write Format                                                           |     |

| DMA Register 10: DMAC1 DMA Command/Mask Register (Write Only) - I/O Address=00AH            | 76  |

| DMA Request Mask Register Write Single Bit Format                                           | 76  |

| DMA Register 11: DMAC1 DMA Mode Register (Write Only) - I/O Address=00BH                    | 76  |

| Mode Register Format                                                                        | 77  |

| DMA Register 12: DMAC1 Address Space Expansion Flip-Flop Control Register (Write Only) -    |     |

| I/O Address=00CH                                                                            |     |

| DMA Register 13: DMAC1 Master Clear Register (Write Only) - I/O Address=00DH                |     |

| DMA Register 14: DMAC1 DMA Mask Clear Register (Write Only) - I/O Address=00EH              |     |

| DMA Register 15: DMAC1 Request Mask Register Control (Read/Write) - I/O Address=00FH        |     |

| DMA Request Mask Register Read and Write All Bits Format                                    | 78  |

| DMA Register 16: DMAC2 Channel 0 (Channel 4) Current Address Register (Read/Write) -        |     |

| I/O Address=0C0H                                                                            | 78  |

| DMA Register 17: DMAC2 Channel 0 (Channel 4) Current Word Count Register (Read/Write) -     |     |

| I/O Address=0C2H                                                                            | 78  |

| DMA Register 18: DMAC2 Channel 1 (Channel 5) Current Address Register (Read/Write) -        |     |

| I/O Address=0C4H                                                                            | 78  |

| DMA Register 19: DMAC2 Channel 1 (Channel 5) Current Word Count Register (Read/Write) -     |     |

| I/O Address=0C6H                                                                            | 79  |

| DMA Register 20: DMAC2 Channel 2 (Channel 6) Current Address Register (Read/Write) -        |     |

| I/O Address=0C8H                                                                            | 79  |

| DMA Register 21: DMAC2 Channel 2 (Channel 6) Current Word Count Register (Read/Write) -     | 70  |

| I/O Address=0CAH                                                                            | / 9 |

| DMA Register 22: DMAC2 Channel 3 (Channel 7) Current Address Register (Read/Write) -        | 70  |

| I/O Address=0CCH                                                                            | / 8 |

| I/O Address=0CEH                                                                            | 70  |

| DMA Register 24: DMAC2 Status/Command Register (Read/Write) - I/O Address=0D0H              |     |

| Status Register Format (Read Only)                                                          |     |

| Command Register Format (Write Only)                                                        |     |

| DMA Register 25: DMAC2 DMA Request Register (Write Only) - I/O Address=0D2H                 |     |

| DMA Request Register Write Format                                                           |     |

| DMA Register 26: DMAC2 DMA Command/Mask Register (Write Only) - I/O Address=0D4H            |     |

| DMA Request Mask Register Write Single Bit Format                                           |     |

| DMA Register 27: DMAC2 DMA Mode Register (Write Only) - I/O Address=0D6H                    |     |

| Mode Register Format                                                                        |     |

| DMA Register 28: DMAC2 Address Space Expansion Flip-Flop Control Register (Write Only) -    |     |

| I/O Address=0D8H                                                                            | 85  |

| DMA Register 29: DMAC2 Master Clear Register (Write Only) - I/O Address=0DAH                |     |

| DMA Register 30: DMAC2 DMA Mask Clear Register (Write Only) - I/O Address=0DCH              |     |

| DMA Register 31: DMAC2 Request Mask Register Control (Read/Write) - I/O Address=0DEH        |     |

| DMA Request Mask Register Read and Write All Bits Format                                    |     |

| DMA Register 32: DMAC1 Channel 2 Page Address Register (Read/Write) - Index=081H            |     |

| DMA Register 33: DMAC1 Channel 3 Page Address Register (Read/Write) - Index=082H            |     |

| DMA Register 34: DMAC1 Channel 1 Page Address Register (Read/Write) - Index=083H            |     |

| DMA Register 35: DMAC1 Channel 0 Page Address Register (Read/Write) - Index=087H            |     |

| DMA Register 36: DMAC2 Channel 6 Page Address Register (Read/Write) - Index=089H            |     |

|                                                                                             |     |

| DMA Register 37: DMAC2 Channel 7 Page Address Register (Read/Write) - Index=08AH                       |     |

|--------------------------------------------------------------------------------------------------------|-----|

| DMA Register 38: DMAC2 Channel 5 Page Address Register (Read/Write) - Index=08BH                       | 85  |

| DMA Register 39: DMAC1 Extended Mode Control (Write Only) – I/O Address=40BH                           | 85  |

| DMAC1 Extended Mode Control Register Format                                                            |     |

| DMA Register 40: DMAC1 Channel 2 High Page Address Register (Read/Write) - Index=481H                  |     |

| DMA Register 41: DMAC1 Channel 3 High Page Address Register (Read/Write) - Index=482H                  |     |

| DMA Register 42: DMAC1 Channel 1 High Page Address Register (Read/Write) - Index=483H                  |     |

| DMA Register 43: DMAC1 Channel 0 High Page Address Register (Read/Write) - Index=487H                  |     |

| DMA Register 44: DMAC2 Channel 6 High Page Address Register (Read/Write) - Index=489H                  |     |

|                                                                                                        |     |

| DMA Register 45: DMAC2 Channel 7 High Page Address Register (Read/Write) - Index=48AH                  |     |

| DMA Register 46: DMAC2 Channel 5 High Page Address Register (Read/Write) - Index=48BH                  |     |

| DMA Register 47: DMAC2 Extended Mode Control (Write Only) - I/O Address=4D6H                           |     |

| DMAC2 Extended Mode Control Register Format                                                            |     |

| CY82C693UB IDE (Bus Mastering) DMA Controller Registers                                                |     |

| SFF-8038i Registers                                                                                    | 87  |

| Bus Master IDE Command Register Format (Offset+00H for Primary Channel;                                |     |

| Offset +08H for Secondary Channel)                                                                     | 87  |

| Bus Master IDE Status Register Format (Offset+02H for Primary Channel;                                 |     |

| Offset +0AH for Secondary Channel)                                                                     | 88  |

| Bus Master IDE Descriptor Table Pointer Register Format                                                |     |

| (Offset+04H-07H for Primary Channel; Offset +0CH-0FH for Secondary Channel)                            | 88  |

| Bus Master IDE I/O Base Address Register (PCI Configuration Space, function 1, register address 20-23H |     |

| hyperCache Specific (Not Required by SFF-8038i) Registers                                              |     |

| Bus Master IDE Channel 0 Configuration Register (I/O Address 22H with Data = 30 (Index Port);          | 00  |

| I/O Address 23H is the Data Port)                                                                      | 00  |

| Bus Master IDE Channel 1 Configuration Register (I/O Address 22H with Data = 31 (Index Port);          | 08  |

|                                                                                                        | 0.0 |

| I/O Address 23H is the Data Port)                                                                      | 88  |

| Bus Master IDE TimeOut Register (I/O Address 22H with Data = 32 (Index Port);                          | 0.0 |

| I/O Address 23H is the Data Port) - Write Only                                                         | 85  |

| Bus Master IDE Test Register (I/O Address 22H with Data = 33 (Index Port);                             |     |

| I/O Address 23H is the Data Port)                                                                      |     |

| CY82C693UB Interrupt Controller Registers                                                              |     |

| ICW1: INTC1 Interrupt Initialization Command Word 1 (Write Only) - I/O Address=020H                    |     |

| ICW2: INTC1 Interrupt Initialization Command Word 2 (Write Only) - I/O Address=021H                    |     |

| ICW3: INTC1 Interrupt Initialization Command Word 3 (Write Only) - I/O Address=021H                    | 92  |

| ICW4: INTC1 Interrupt Initialization Command Word 4 (Write Only) - I/O Address=021H                    | 92  |

| ICW1: INTC2 Interrupt Initialization Command Word 1 (Write Only) - I/O Address=0A0H                    |     |

| ICW2: INTC2 Interrupt Initialization Command Word 2 (Write Only) - I/O Address=0A1H                    |     |

| ICW3: INTC2 Interrupt Initialization Command Word 3 (Write Only) - I/O Address=0A1H                    |     |

| ICW4: INTC2 Interrupt Initialization Command Word 4 (Write Only) - I/O Address=0A1H                    |     |

| OCW1: INTC1 Interrupt Operational Command Word 1 (Read/Write) - I/O Address=021H                       |     |

| OCW2: INTC1 Interrupt Operational Command Word 2 (Write Only) - I/O Address=020H                       |     |

| OCW3: INTC1 Interrupt Operational Command Word 3 (Write Only) - I/O Address=020H                       |     |

|                                                                                                        |     |

| OCW1: INTC2 Interrupt Operational Command Word 1 (Read/Write) - I/O Address=0A1H                       |     |

| OCW2: INTC2 Interrupt Operational Command Word 2 (Write Only) - I/O Address=0A0H                       |     |

| OCW3: INTC2 Interrupt Operational Command Word 3 (Write Only) - I/O Address=0A0H                       |     |

| CY82C693UB Timer/Counter Registers                                                                     |     |

| Timer/Counter Register 0: Timer Control Word Register (Write Only) - Address=043H                      |     |

| Timer Control Word Register Format (Not Read-Back Command or Counter Latch Command)                    |     |

| Timer Control Word Register Format (Read-Back Command)                                                 |     |

| Timer Control Word Register Format (Counter Latch Command)                                             | 98  |

| Timer/Counter Register 1: Counter 0 Register (Read/Write Except for Read-Back Status Command)                     |     |

|-------------------------------------------------------------------------------------------------------------------|-----|

| - Address=040H                                                                                                    | 99  |

| Counter 0 Register Format (Read-Back Status Command – Read Only)                                                  |     |

| Timer/Counter Register 2: Counter 1 Register (Read/Write Except for Read-Back Status Command)                     |     |

| - Address=041H                                                                                                    |     |

| Counter 1 Register Format (Read-Back Status Command – Read Only)                                                  |     |

| Timer/Counter Register 3: Counter 2 Register (Read/Write Except for Read-Back Status Command)                     |     |

| - Address=042H                                                                                                    |     |

| Counter 2 Register Format (Read-Back Status Command – Read Only)                                                  |     |

| CY82C693UB Real-Time-Clock Registers                                                                              |     |

| RTC Register 0: Seconds Byte (Read/Write except for bit 7 which is always 0) - Index=00H                          |     |

| RTC Register 1: Seconds Alarm (Read/Write) - Index=01H                                                            |     |

| RTC Register 2: Minutes Byte (Read/Write) - Index=02H                                                             |     |

| RTC Register 3: Minutes Alarm (Read/Write) - Index=03H                                                            |     |

| RTC Register 4: Hours Byte (Read/Write) - Index=04H                                                               |     |

| RTC Register 5: Hours Alarm (Read/Write) - Index=05H                                                              |     |

| RTC Register 6: Day-of-the-Week Byte (Read/Write) - Index=06H                                                     |     |

| RTC Register 7: Day-of-the-Month Byte (Read/Write) - Index=07HRTC Register 8: Month Byte (Read/Write) - Index=08H |     |

| RTC Register 6: Month Byte (Read/Write) - Index=06H                                                               |     |

| RTC Register 10: Control/Status Register A (Read/Write except for bit 7 which is Read Only)                       | 102 |

| - Index=0AH                                                                                                       | 100 |

| RTC Register 11: Control/Status Register B (Read/Write) - Index=0BH                                               |     |

| RTC Register 12: Control/Status Register C (Read Only) - Index=0CH                                                |     |

| RTC Register 13: Control/Status Register D (Read Only) - Index=0DH                                                |     |

| RTC Registers 14-127: Battery-Backable Scratch Block 1 (Read/Write) – Indices=0EH-7FH                             |     |

| RTC Registers 128-255: Battery-Backable Scratch Block 2 (Read/Write) – Indices=80H-FFH                            |     |

| CY82C693UB Keyboard/Mouse Controller Registers                                                                    |     |

| Keyboard/Mouse Register 0: Status Register (Read Only) - I/O Read to address 64H                                  |     |

| Keyboard/Mouse Register 1: Command Byte Register                                                                  |     |

| System to Controller Command Set                                                                                  |     |

| Controller to System Command Set                                                                                  | 108 |

| System to Keyboard Command Set                                                                                    | 109 |

| Keyboard to System Command Set                                                                                    |     |

| System to Mouse Controller Command Set                                                                            | 110 |

| Mouse to System Controller Command Set                                                                            |     |

| CY82C693UB PCI Configuration Registers                                                                            |     |

| PCI to ISA PCI Configuration Registers (Function 0 during Configuration Cycle)                                    | 112 |

| Register 0: Vendor ID Number (Read Only) - Index=00H with a 16-bit access                                         | 112 |

| Register 1: Device ID Number (Read Only) - Index=02H with a 16-bit access                                         | 112 |

| Register 3: Command Register (Read/Write) - Index=04H with a 16-bit access                                        |     |

| Register 4: Status Register (Read/Write) - Index=06H with a 16-bit access                                         |     |

| Register 5: Revision ID Number (Read Only) - Index=08H with an 8-bit access                                       |     |

| Register 6: Programming Interface Revision ID Number (Read Only) - Index=09H with an 8-bit acce                   |     |

| Register 7: Sub Class Code Register (Read Only) - Index=0AH with an 8-bit access                                  |     |

| Register 8: Base Class Code Register (Read Only) - Index=0BH with an 8-bit access                                 |     |

| Register 9: Header Type Register (Read Only) - Index=0EH with an 8-bit access                                     |     |

| Register 10: PCI Interrupt A Routing Control Register (Read/Write) - Index=40H with an 8-bit access               |     |

| Register 11: PCI Interrupt B Routing Control Register (Read/Write) - Index=41H with an 8-bit access               |     |

| Register 12: PCI Interrupt C Routing Control Register (Read/Write) - Index=42H with an 8-bit access               |     |

| Register 13: PCI Interrupt D Routing Control Register (Read/Write) - Index=43H with an 8-bit access               |     |

| Register 14: PCI Control Register (Read/Write) - Index=44H with an 8-bit access                                   | 115 |

| Register 15: PCI Error Control Register (Read/Write) - Index=45H with an 8-bit access                | 116    |

|------------------------------------------------------------------------------------------------------|--------|

| Register 16: PCI Error Status Register (Read/Write) - Index=46H with an 8-bit access                 | 116    |

| Register 17: PCI BIOS Control Register (Read/Write) - Index=47H with an 8-bit access                 | 117    |

| Register 18: ISA/DMA Top of Memory Control (Read/Write) - Index=48H with an 8-bit access             | 117    |

| Register 19: AT Control Register #1 (Read/Write) - Index=49H with an 8-bit access                    | 118    |

| Register 20: AT Control Register #2 (Read/Write) - Index=4AH with an 8-bit access                    | 118    |

| Register 21: PCI IDE Interrupt Request 0 Routing Control Register (Read/Write) -                     |        |

| Index=4BH with an 8-bit access                                                                       | 119    |

| Register 22: PCI IDE Interrupt Request 1 Routing Control Register (Read/Write) -                     |        |

| Index=4CH with an 8-bit access                                                                       |        |

| Register 23: CY82C693UB Stand-Alone Control and USB Host Controller Control Register (Read/Write     |        |

| - Index=4DH with an 8-bit access                                                                     |        |

| Register 24: CY82C693UB USB Control Register 1 (Read/Write) - Index=4EH with an 8-bit access         |        |

| Register 24: CY82C693UB USB Control Register 2 (Read/Write) - Index=4FH with an 8-bit access         | 121    |

| Primary Channel IDE PIO (Programmed I/O)                                                             |        |

| PCI Configuration Registers (Function 1 during Configuration Cycle)                                  | 122    |

| Register 0: Vendor ID Number (Read Only) - Index=00H with a 16-bit access                            | 122    |

| Register 1: Device ID Number (Read Only) - Index=02H with a 16-bit access                            | 122    |

| Register 2: Command Register (Read/Write) - Index=04H with a 16-bit access                           | 122    |

| Register 3: Status Register (Read/Write) - Index=06H with a 16-bit access                            | 123    |

| Register 4: Revision ID Number (Read Only) - Index=08H with an 8-bit access                          | 123    |

| Register 5: Class Code Register (Read Only) - Index=09H with a 32-bit access                         | 123    |

| Register 6: Header Type Register (Read Only) - Index=0EH with an 8-bit access                        | 123    |

| Register 7: Primary IDE Command Address Register (Read/Write) - Index=10H with a 32-bit access       | 123    |

| Register 8: Primary IDE Control Address Register (Read/Write) - Index=14H with a 32-bit access       | 124    |

| Register 9: Primary Bus Master IDE Control Address Register (Read/Write) -                           |        |

| Index=20H with a 32-bit access                                                                       | 124    |

| Register 10: Primary IDE Interrupt INTA Control Register (Read/Write) - Index=3CH with an 8-bit acce | ss 124 |

| Register 11: Primary IDE Interrupt Pin Control Register (Read Only) - Index=3DH with an 8-bit access | 124    |

| Register 12: Primary IDE Control Register (Read/Write) - Index=40H with a 32-bit access              | 125    |

| Register 13: Primary IDE Address Setup Control Register (Read/Write) - Index=48H with a 32-bit acce  | ss 125 |

| Register 14: Primary Master Drive IDE IOR Command Control Register (Read/Write) -                    |        |

| Index=4CH with an 8-bit access                                                                       | 125    |

| Register 15: Primary Master Drive IDE IOW Command Control Register (Read/Write) -                    |        |

| Index=4DH with an 8-bit access                                                                       | 126    |

| Register 16: Primary Slave Drive IDE IOR Command Control Register (Read/Write) -                     |        |

| Index=4EH with an 8-bit access                                                                       | 126    |

| Register 17: Primary Slave Drive IDE IOW Command Control Register (Read/Write) -                     |        |

| Index=4FH with an 8-bit access                                                                       | 126    |

| Register 18: Primary Master Drive 8-Bit IDE Command Control Register (Read/Write) -                  |        |

| Index=50H with an 8-bit access                                                                       | 126    |

| Register 19: Primary Slave Drive 8-Bit IDE Command Control Register (Read/Write) -                   |        |

| Index=51H with an 8-bit access                                                                       | 126    |

| Register 20: Primary Master Drive IORDY Control Register (Read/Write) -                              |        |

| Index=52H with an 8-bit access                                                                       | 127    |

| Register 21: Primary Slave Drive IORDY Control Register (Read/Write) -                               |        |

| Index=53H with an 8-bit access                                                                       | 127    |

| Secondary Channel IDE PIO (Programmed I/O)                                                           |        |

| PCI Configuration Registers (Function 2 during Configuration Cycle)                                  |        |

| Register 0: Vendor ID Number (Read Only) - Index=00H with a 16-bit access                            |        |

| Register 1: Device ID Number (Read Only) - Index=02H with a 16-bit access                            |        |

| Register 2: Command Register (Read/Write) - Index=04H with a 16-bit access                           | 128    |

| Register 3: Status Register (Read/Write) - Index=06H with a 16-bit access                            |         |

|------------------------------------------------------------------------------------------------------|---------|

| Register 4: Revision ID Number (Read Only) - Index=08H with an 8-bit access                          | 129     |

| Register 5: Class Code Register (Read Only) - Index=09H with a 32-bit access                         | 129     |

| Register 6: Header Type Register (Read Only) - Index=0EH with an 8-bit access                        |         |

| Register 7: Secondary IDE Command Address Register (Read/Write) - Index=10H with a 32-bit acces      |         |

| Register 8: Secondary IDE Control Address Register (Read/Write) - Index=14H with a 32-bit access .   | 130     |

| Register 9: Secondary IDE Interrupt INTB Control Register (Read/Write) -                             |         |

| Index=3CH with an 8-bit access                                                                       |         |

| Register 10: Secondary IDE Interrupt Pin Control Register (Read Only) - Index=3DH with an 8-bit acce | ess 130 |

| Register 11: Secondary IDE Control Register (Read/Write) - Index=40H with a 32-bit access            | 130     |

| Register 12: Secondary IDE Address Setup Control Register (Read/Write) -                             |         |

| Index=48H with a 32-bit access                                                                       | 131     |

| Register 13: Secondary Master Drive IDE IOR Command Control Register (Read/Write) -                  |         |

| Index=4CH with an 8-bit access                                                                       | 131     |

| Register 14: Secondary Master Drive IDE IOW Command Control Register (Read/Write) -                  |         |

| Index=4DH with an 8-bit access                                                                       | 131     |

| Register 15: Secondary Slave Drive IDE IOR Command Control Register (Read/Write) -                   |         |

| Index=4EH with an 8-bit access                                                                       | 131     |

| Register 16: Secondary Slave Drive IDE IOW Command Control Register (Read/Write) -                   |         |

| Index=4FH with an 8-bit access                                                                       | 131     |

| Register 17: Secondary Master Drive 8-Bit IDE Command Control Register (Read/Write) -                |         |

| Index=50H with an 8-bit access                                                                       | 132     |

| Register 18: Secondary Slave Drive 8-Bit IDE Command Control Register (Read/Write) -                 |         |

| Index=51H with an 8-bit access                                                                       | 132     |

| Register 19: Secondary Master Drive IORDY Control Register (Read/Write) -                            |         |

| Index=52H with an 8-bit access                                                                       |         |

| USB Host Controller PCI Configuration Registers (Function 3 during Configuration Cycle)              |         |

| Register 0: Vendor ID Number (Read Only) - Index=00H with a 16-bit access                            |         |

| Register 1: Device ID Number (Read Only) - Index=02H with a 16-bit access                            |         |

| Register 2: Command Register (Read/Write) - Index=04H with a 16-bit access                           |         |

| Register 3: Status Registers (Read/Write) - Index=06H with a 16-bit access                           |         |

| Register 4: Revision ID Number (Read Only) - Index=08H with an 8-bit access                          |         |

| Register 5: Class Code Register (Read Only) - Index=09H with a 24-bit access                         |         |

| Register 6: Cache Line Size (Read/Write) - Index=0CH with an 8-bit access                            |         |

| Register 7: Latency Timer (Read/Write) - Index=0DH with an 8-bit access                              |         |

| Register 8: Header Type Register (Read Only) - Index=0EH with an 8-bit access                        |         |

| Register 9: BIST Register (Read Only) - Index=0FH with an 8-bit access                               |         |

| Register 10: Base Address Register (Read/Write) - Index=10H with a 32-bit access                     |         |

| Register 11: Interrupt Line Register (Read/Write) - Index=3CH with an 8-bit access                   |         |

| Register 12: Interrupt Pin Register (Read/Write) - Index=3DH with an 8-bit access                    |         |

| Register 13: Min_Gnt Register (Read Only) - Index=3EH with an 8-bit access                           |         |

| Register 14: Max_Lat Register (Read Only) - Index=3FD with an 8-bit access                           |         |

| Register 15: ASIC Test Mode Enable Register (Read/Write) - Index=40H with a 32-bit access            |         |

| Register 16: ASIC Operational Mode Enable Register (Read/Write) - Index=44H with an 8-bit access .   |         |

| USB Host Controller Operational Registers                                                            |         |

| Register 0: HcRevision (Read Only) - Offset=00H with a 32-bit access                                 |         |

| Register 1: HcControl (Read/Write) - Offset=04H with a 32-bit access                                 |         |

| Register 2: HcCommandStatus (Read/Write) - Offset=08H with a 32-bit access                           |         |

| Register 3: HcInterruptStatus (Read/Write) - Offset=0CH with a 32-bit access                         |         |

| Register 4: HcInterruptEnable (Read/Write) - Offset=10H with a 32-bit access                         |         |

| Register 5: HcInterruptDisable (Read/Write) - Offset=14H with a 32-bit access                        |         |

| Register 6: HcHCCA (Read/Write) - Offset=18H with a 32-bit access                                    | 140     |

| Register 7: HcPeriodCurrentED (Read/Write) - Offset=1CH with a 32-bit access        | 140 |

|-------------------------------------------------------------------------------------|-----|

| Register 8: HcControlHeadED (Read/Write) - Offset=20H with a 32-bit access          | 140 |

| Register 9: HcControlCurrentED (Read/Write) - Offset=24H with a 32-bit access       | 141 |

| Register 10: HcBulkHeadED (Read/Write) - Offset=28H with a 32-bit access            | 141 |

| Register 11: HcBulkCurrentED (Read/Write) - Offset=2CH with a 32-bit access         | 141 |

| Register 12: HcDoneHead (Read/Write) - Offset=30H with a 32-bit access              | 141 |

| Register 13: HcFmInterval (Read/Write) - Offset=34H with a 32-bit access            | 141 |

| Register 13: HcFrameRemaining (Read Only) - Offset=38H with a 32-bit access         | 141 |

| Register 14: HcFmNumber (Read Only) - Offset=3CH with a 32-bit access               | 142 |

| Register 15: HcPeriodicStart (Read/Write) - Offset=40H with a 32-bit access         |     |

| Register 16: HcLSThreshold (Read/Write) - Offset=44H with a 32-bit access           |     |

| Register 17: HcRhDescriptorA (Read/Write) - Offset=48H with a 32-bit access         | 142 |

| Register 18: HcRhDescriptorB (Read/Write) - Index=4CH with a 32-bit access          |     |

| Register 19: HcRhStatus (Read/Write) - Index=50H with a 32-bit access               |     |

| Register 20: HcRhPortStatus[1:2] (Read/Write) - Index=54H, 58H with a 32-bit access | 145 |

| Register 21: HceControl (Read/Write) - Index=100H with a 32-bit access              |     |

| Register 22: HceInput - Index=104H with a 32-bit access                             |     |

| Register 23: HceOutput - Index=108H with a 32-bit access                            |     |

| Register 24: HceStatus (Read/Write) - Index=10CH with a 32-bit access               |     |

| Maximum Ratings                                                                     | 148 |

| Electrical Characteristics                                                          | 148 |

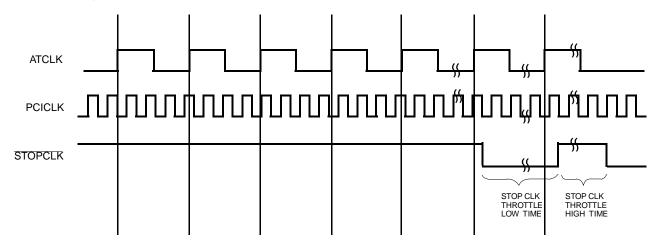

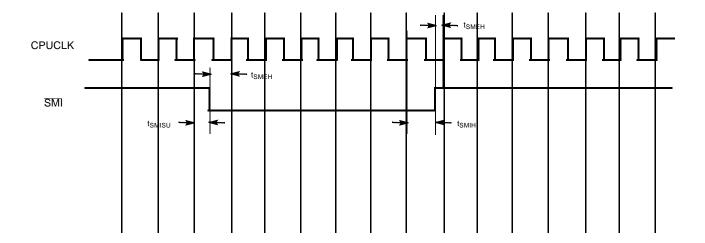

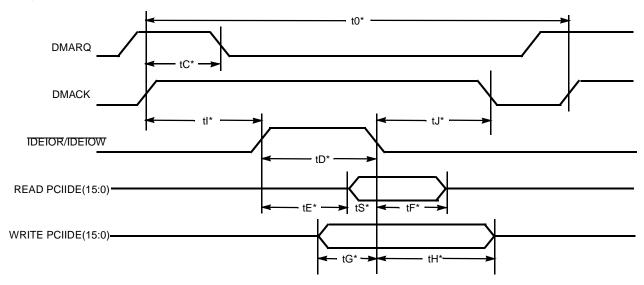

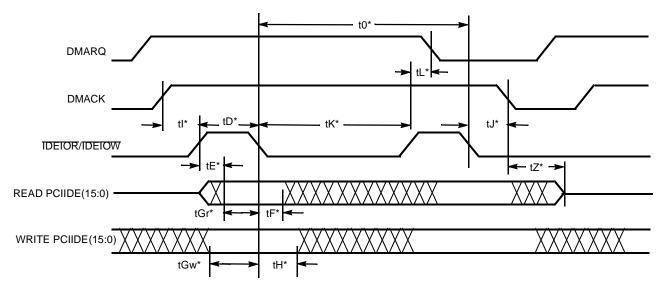

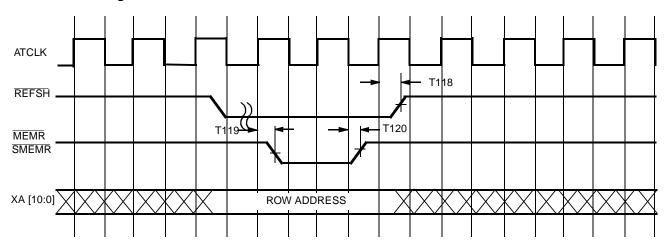

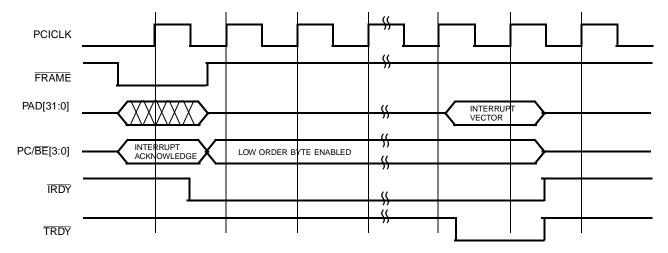

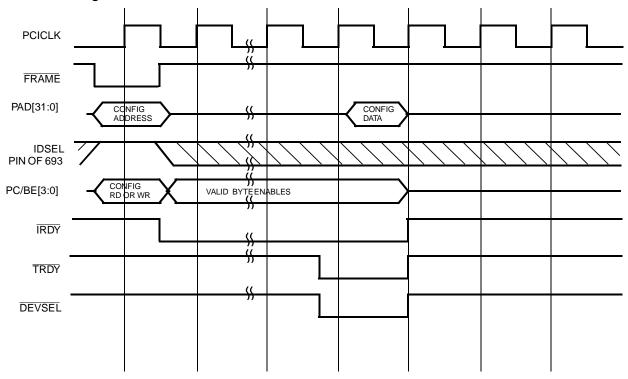

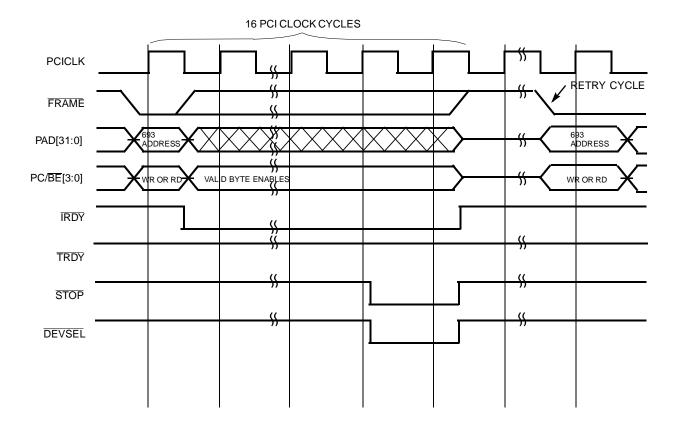

| Switching Waveforms                                                                 | 149 |

| Ordering Information                                                                | 163 |

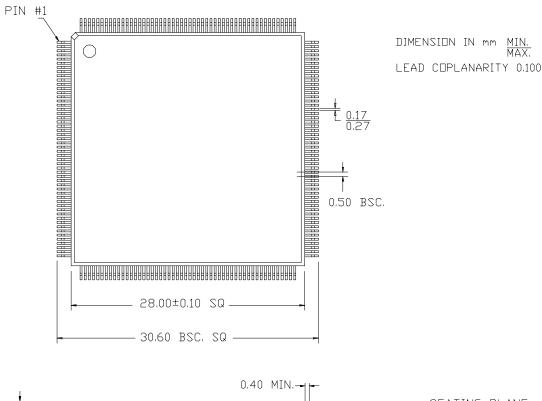

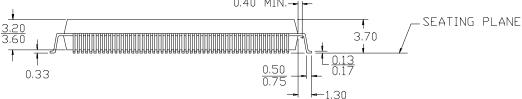

| Package Diagrams                                                                    | 164 |

|                                                                                     |     |

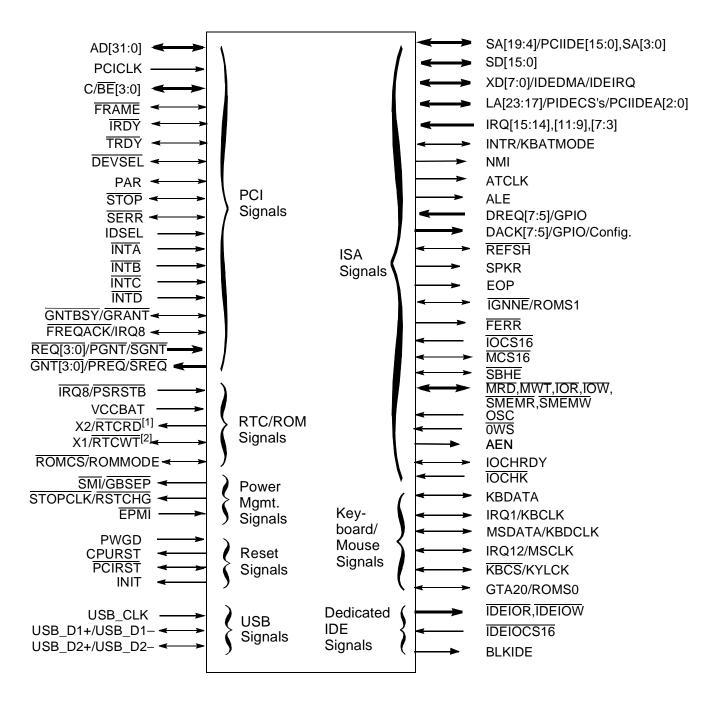

#### CY82C693UB Signals

NOTES: 1. RTCRD available only as bond option.

2. RTCWT available only as bond option.

82C693UB-2

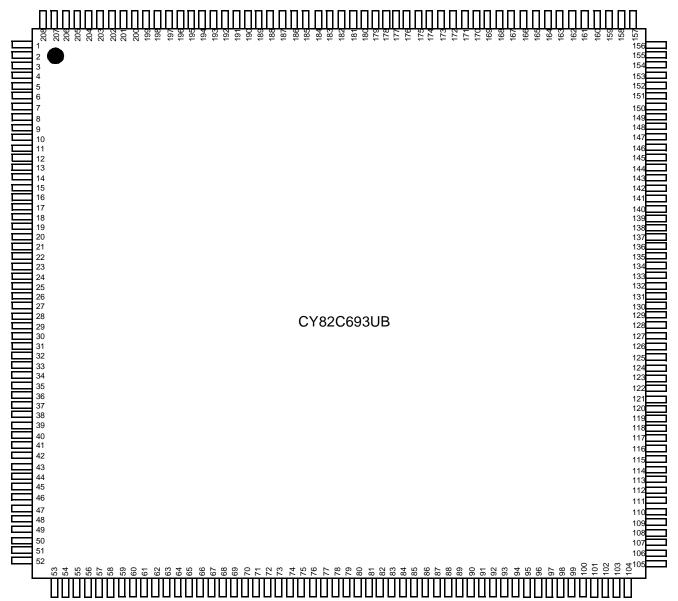

# **Pin Configuration**

82C693UB-2

# CY82C693UB Pin Reference (In Numerical Order by Pin Number)

| Pin<br># | Pin Name | Pin<br># | Pin Name       | Pin<br># | Pin Name                 | Pin<br># | Pin Name                   | Pin<br># | Pin Name           |  |

|----------|----------|----------|----------------|----------|--------------------------|----------|----------------------------|----------|--------------------|--|

| 1        | GND      | 43       | AD9            | 85       | SA7/IDE3                 | 127      | X1/RTCWT(bond option only) | 169      | +3.3V              |  |

| 2        | FRAME    | 44       | AD8            | 86       | SA6/IDE2                 | 128      | PWGD                       | 170      | GTA20/ROMS0        |  |

| 3        | IDSEL    | 45       | AD7            | 87       | SA5/IDE1                 | 129      | DRQ0                       | 171      | GND                |  |

| 4        | TRDY     | 46       | AD6            | 88       | SA4/IDE0                 | 130      | DRQ5/GPIO6/<br>PWREN       | 172      | STOPCLK/<br>RSTCHG |  |

| 5        | ĪRDY     | 47       | AD5            | 89       | SA3                      | 131      | DRQ6/GPIO7/<br>OVRCUR      | 173      | CPURST             |  |

| 6        | DEVSEL   | 48       | AD4            | 90       | SA2                      | 132      | DRQ7/GPIO8/<br>SMIACT      | 174      | INIT               |  |

| 7        | SERR     | 49       | AD3            | 91       | SA1                      | 133      | OSC                        | 175      | NMI                |  |

| 8        | PAR      | 50       | AD2            | 92       | SA0                      | 134      | SD0                        | 176      | INTR/<br>KBATMODE  |  |

| 9        | USB_D1+  | 51       | AD1            | 93       | GND                      | 135      | SD1                        | 177      | IGNNE/ROMS1        |  |

| 10       | USB_D1-  | 52       | AD0            | 94       | ROMCS/<br>ROMMODE        | 136      | +5V                        | 178      | FERR               |  |

| 11       | C/BE3    | 53       | GND            | 95       | IRQ7                     | 137      | GND                        | 179      | SMI/GBSEP          |  |

| 12       | C/BE2    | 54       | IOCHK          | 96       | IRQ6                     | 138      | SD2                        | 180      | USB_D2+            |  |

| 13       | C/BE1    | 55       | IOCHRDY        | 97       | IRQ5                     | 139      | SD3                        | 181      | USB_D2-            |  |

| 14       | C/BE0    | 56       | <del>0WS</del> | 98       | IRQ4                     | 140      | SD4                        | 182      | EPMI               |  |

| 15       | USB_CLK  | 57       | AEN            | 99       | IRQ3                     | 141      | SD5                        | 183      | MSDATA/<br>KBDCLK  |  |

| 16       | AD31     | 58       | SMEMW          | 100      | IRQ1/KBCLK               | 142      | SD6                        | 184      | KBCS/KYLCK         |  |

| 17       | AD30     | 59       | SMEMR          | 101      | REFSH                    | 143      | SD7                        | 185      | KBDATA             |  |

| 18       | AD29     | 60       | IOW            | 102      | IRQ9                     | 144      | MRD                        | 186      | IDEIOCS16          |  |

| 19       | AD28     | 61       | ĪŌR            | 103      | ALE                      | 145      | MWT                        | 187      | IDEIOW             |  |

| 20       | +5V      | 62       | LA23/IDECS0    | 104      | +5V                      | 146      | SD15                       | 188      | IDEIOR             |  |

| 21       | GND      | 63       | LA22/IDECS1    | 105      | GND                      | 147      | SD14                       | 189      | GNTBSY/<br>GRANT   |  |

| 22       | AD27     | 64       | LA21/SIDECS0   | 106      | IRQ10                    | 148      | SD13                       | 190      | FREQACK/IRQ8       |  |

| 23       | AD26     | 65       | +5V            | 107      | ATCLK                    | 149      | SD12                       | 191      | GNT0/PREQ          |  |

| 24       | AD25     | 66       | LA20/SIDECS1   | 108      | IRQ11                    | 150      | SD11                       | 192      | GNT1/SREQ          |  |

| 25       | AD24     | 67       | GND            | 109      | IRQ12/MSCLK              | 151      | GND                        | 193      | GNT2/SQWV          |  |

| 26       | AD23     | 68       | LA19/IDEA2     | 110      | IRQ14                    | 152      | SD10                       | 194      | GNT3/DISARB        |  |

| 27       | AD22     | 69       | LA18/IDEA1     | 111      | IRQ15                    | 153      | SD9                        | 195      | +5V                |  |

| 28       | AD21     | 70       | LA17/IDEA0     | 112      | DACK0/TSTM               | 154      | SD8                        | 196      | REQ0/PGNT          |  |

| 29       | AD20     | 71       | GND            | 113      | DACK1/TSTM0              | 155      | XD0/XDIR                   | 197      | GND                |  |

| 30       | AD19     | 72       | SA19/IDE15     | 114      | DACK2/TSTM1              | 156      | +5V                        | 198      | REQ1/SGNT          |  |

| 31       | AD18     | 73       | SA18/IDE14     | 115      | DACK3/<br>DISPSEL        | 157      | BLKIDE                     | 199      | REQ2               |  |

| 32       | +5V      | 74       | SA17/IDE13     | 116      | DACK5/KB-<br>SEL/GPIO9   | 158      | XD1/XDEN                   | 200      | REQ3               |  |

| 33       | GND      | 75       | SA16/IDE12     | 117      | DACK6/RTC-<br>SEL/GPIO10 | 159      | XD2/IACK1                  | 201      | PCIRST             |  |

| 34       | AD17     | 76       | SA15/IDE11     | 118      | DACK7/EXT-<br>BUF/GPIO11 | 160      | XD3/IREQ1                  | 202      | ĪNTD               |  |

# CY82C693UB Pin Reference (In Numerical Order by Pin Number) (continued)

**PRELIMINARY**

| Pin<br># | Pin Name | Pin<br># | Pin Name   | Pin<br># | Pin Name                          | Pin<br># | Pin Name                   | Pin<br># | Pin Name |

|----------|----------|----------|------------|----------|-----------------------------------|----------|----------------------------|----------|----------|

| 35       | AD16     | 77       | SA14/IDE10 | 119      | EOP                               | 161      | XD4/IACK0                  | 203      | INTC     |

| 36       | AD15     | 78       | SA13/IDE9  | 120      | DRQ1                              | 162      | XD5/IREQ0                  | 204      | INTB     |

| 37       | AD14     | 79       | SA12/IDE8  | 121      | DRQ3                              | 163      | XD6/IDEIRQ1/<br>GPIO1/BUSY | 205      | INTA     |

| 38       | AD13     | 80       | SA11/IDE7  | 122      | DRQ2                              | 164      | XD7/IDEIRQ0/<br>GPIO0      | 206      | STOP     |

| 39       | AD12     | 81       | GND        | 123      | ĪRQ8/PSRSTB                       | 165      | SBHE                       | 207      | PCICLK   |

| 40       | AD11     | 82       | SA10/IDE6  | 124      | VCCBAT                            | 166      | MCS16                      | 208      | +5V      |

| 41       | AD10     | 83       | SA9/IDE5   | 125      | GND                               | 167      | IOCS16                     |          |          |

| 42       | GND      | 84       | SA8/IDE4   | 126      | X2/RTCRD<br>(bond option<br>only) | 168      | SPKR                       |          |          |

# CY82C693UB Pin Reference (In Alphabetical Order by Signal Name)

| Pin  | Pin |                          |         |                   | Pin       |                   | Pin |                    |         |

|------|-----|--------------------------|---------|-------------------|-----------|-------------------|-----|--------------------|---------|

| Name | No. | Pin Name                 | Pin No. | Pin Name          | No.       | Pin Name          | No. | Pin Name           | Pin No. |

| AD0  | 52  | C/BE3                    | 11      | INTR/<br>KBATMODE | 176   SD8 |                   | SD8 | 154                |         |

| AD1  | 51  | CPURST                   | 173     | IOCHK             | 54        |                   |     | SD9                | 153     |

| AD2  | 50  | DACKO/TSTM               | 114     | IOCHRDY           | 55        | PWGD              | 128 | SD10               | 152     |

| AD3  | 49  | DACK1/TSTM0              | 114     | IOCS16            | 167       | REFSH             | 101 | SD11               | 150     |

| AD4  | 48  | DACK2/TSTM1              | 114     | IOR               | 61        | REQ0/<br>PGNT     | 196 | SD12               | 149     |

| AD5  | 47  | DACK3 /<br>DISPSEL       | 115     | IOW               | 60        | REQ17<br>SGNT     | 198 | SD13               | 148     |

| AD6  | 46  | DACK5/<br>KBSEL/GPIO9    | 116     | IRDY              | 5         | REQ2              | 199 | SD14               | 147     |

| AD7  | 45  | DACK6/RTC-<br>SEL/GPIO10 | 117     | IRQ1/KBCLK        | 100       | REQ3              | 200 | SD15               | 146     |

| AD8  | 44  | DACK7/EXT-<br>BUF/GPIO11 | 118     | IRQ3              | 99        | ROMCS/<br>ROMMODE | 94  | SERR               | 7       |

| AD9  | 43  | DEVSEL                   | 6       | IRQ4              | 98        |                   |     | SMEMR              | 59      |

| AD10 | 41  | DRQ0                     | 129     | IRQ5              | 97        | SA0               | 92  | SMEMW              | 58      |

| AD11 | 40  | DRQ1                     | 120     | IRQ6              | 96        | SA1               | 91  | SMI/GBSEP          | 179     |

| AD12 | 39  | DRQ2                     | 122     | IRQ7              | 95        | SA2               | 90  | SPKR               | 168     |

| AD13 | 38  | DRQ3                     | 121     | IRQ8/PSRSTB       | 123       | SA3               | 89  | STOP               | 206     |

| AD14 | 37  | DRQ5/GPIO6/<br>PWREN     | 130     | IRQ9              | 102       | SA4/IDE0          | 88  | STOPCLK/<br>RSTCHG | 172     |

| AD15 | 36  | DRQ6/GPIO7/<br>OVRCUR    | 131     | IRQ10             | 106       | SA5/IDE1          | 87  | TRDY               | 4       |

| AD16 | 35  | DRQ7/GPIO8/<br>SMIACT    | 132     | IRQ11             | 108       | SA6/IDE2          | 86  | USB_CLK            | 15      |

| AD17 | 34  | EOP                      | 119     | IRQ12/MSCLK       | 109       | SA7/IDE3          | 85  | USB_D1+            | 9       |

| AD18 | 31  | ЕРМІ                     | 182     | IRQ14             | 110       | SA8/IDE4          | 84  | USB_D1-            | 10      |

| AD19 | 30  | FERR                     | 178     | IRQ15             | 111       | SA9/IDE5          | 83  | USB_D2+            | 180     |

| AD20 | 29  | FRAME                    | 2       | KBCS/KYLCK        | 184       | SA10/IDE6         | 82  | USB_D2-            | 181     |

# CY82C693UB Pin Reference (In Alphabetical Order by Signal Name) (continued)

| Pin<br>Name | Pin<br>No. | Pin Name         | Pin No.                                                                   | Pin Name          | Pin<br>No. | Pin Name       | Pin<br>No. | Pin Name                    | Pin No.                                  |

|-------------|------------|------------------|---------------------------------------------------------------------------|-------------------|------------|----------------|------------|-----------------------------|------------------------------------------|

| AD21        | 28         | FREQACK/<br>IRQ8 | 190                                                                       | KBDATA            | 185        | SA11/IDE7      | 80         | VCCBAT                      | 124                                      |

| AD22        | 27         | GND              | 1,21,33,<br>42,53,<br>67,71,<br>81,93,<br>105,125,<br>137,151,<br>171,197 | LA17/IDEA0        | 70         | SA12/IDE8      | 79         | X1/RTCWT (bond option only) | 127                                      |

| AD23        | 26         | GNT0/PREQ        | 191                                                                       | LA18/IDEA1        | 69         | SA13/IDE9      | 78         | X2/RTCRD (bond option only) | 126                                      |

| AD24        | 25         | GNT1/SREQ        | 192                                                                       | LA19/IDEA2        | 68         | SA14/IDE10     | 77         | XD0/XDIR                    | 155                                      |

| AD25        | 24         | GNT2/SQWV        | 193                                                                       | LA20/SIDECS1      | 66         | SA15/IDE11     | 76         | XD1/XDEN                    | 158                                      |

| AD26        | 23         | GNT3/DISARB      | 194                                                                       | LA21/SIDECS0      | 64         | SA16/IDE12     | 75         | XD2/IACK1                   | 159                                      |

| AD27        | 22         | GNTBSY/<br>GRANT | 189                                                                       | LA22/IDECS1       | 63         | SA17/IDE13     | 74         | XD3/IREQ1                   | 160                                      |

| AD28        | 19         | GTA20/ROMS0      | 170                                                                       | LA23/IDECS0       | 62         | SA18/IDE14     | 73         | XD4/IACK0                   | 161                                      |

| AD29        | 18         | IDEIOCS16        | 186                                                                       |                   |            | SA19/<br>IDE15 | 72         | XD5/IREQ0                   | 162                                      |

| AD30        | 17         | IDEIOR           | 188                                                                       | MCS16             | 166        | SBHE           | 165        | XD6/IDEIRQ1/<br>GPIO1/BUSY  | 163                                      |

| AD31        | 16         | IDEIOW           | 187                                                                       | MRD               | 144        | SD0            | 134        | XD7/IDEIRQ0/<br>GPIO0       | 164                                      |

| AEN         | 57         | IDSEL            | 3                                                                         | MSDATA/<br>KBDCLK | 183        | SD1            | 135        | ows                         | 56                                       |

| ALE         | 103        | IGNNE/ROMS1      | 177                                                                       | MWT               | 145        | SD2            | 138        | +3.3V                       | 169                                      |

| ATCLK       | 107        | INIT             | 174                                                                       | NMI               | 175        | SD3            | 139        | +5V                         | 20,32,<br>65,104,<br>136,156,<br>195,208 |

| BLKIDE      | 157        | INTA             | 205                                                                       | OSC               | 133        | SD4            | 140        |                             |                                          |

| C/BE0       | 14         | INTB             | 204                                                                       | PAR               | 8          | SD5            | 141        |                             |                                          |

| C/BE1       | 13         | INTC             | 203                                                                       | PCICLK            | 207        | SD6            | 142        |                             |                                          |

| C/BE2       | 12         | ĪNTD             | 202                                                                       | PCIRST            | 201        | SD7            | 143        |                             |                                          |

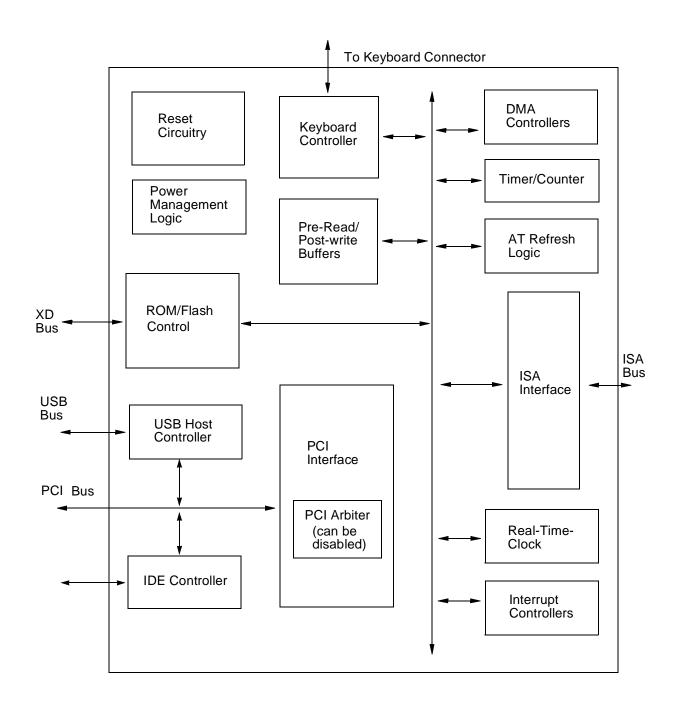

Figure 1. CY82C693UB Functional Block Diagram

#### Introduction

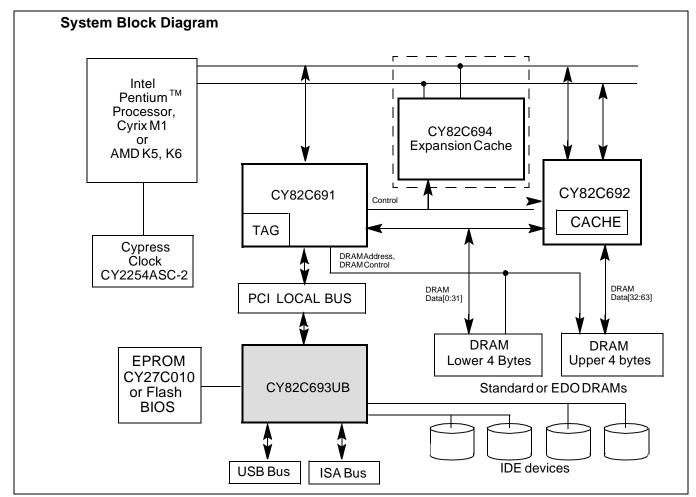

#### **System Overview**

The hyperCache™ family is a family of chips created to provide flexible solutions for today's PC designs. The chipset provides all the functions necessary to implement a 3.3V Pentium-class processor based system with the USB (Universal Serial Bus), PCI (Peripheral Component Interconnect), and the ISA (Industry Standard Architecture) buses. System designers can exploit the advantages of the USB and PCI buses while maintaining access to the large base of ISA cards in the marketplace.

The Cypress hyperCache family offers system designers several key advantages. With only three chips, a complete system can be implemented. Cache can be added up to 512 MB with additional CY82C694 devices in 128-KB increments All chipset solutions are pin-compatible and provide flexible upgrade paths through on-board or external cache modules. Six banks of page-mode or EDO DRAM further increase the system designer's options. The chipset also contains concurrent bus support, PCI enhanced IDE with CD-ROM support, integrated RTC, integrated peripheral control (Interrupts/DMA), and integrated keyboard controller. This chipset is flexible enough to provide the system designer with many cost/performance/function options to provide an optimum solution for a given design.

#### CY82C693UB Introduction

The CY82C693UB Peripheral Controller provides a highly integrated peripheral solution for PCI-based motherboards. The CY82C693UB contains a PCI to ISA bridge, a PCI IDE controller, DMA controllers, Interrupt controllers, a Real-Time-Clock, Keyboard controller and a USB Host Controller.

Figure 1 shows a block diagram of the CY82C693UB.

#### **Functional Overview**

The CY82C693UB Peripheral Controller contains the following functional blocks:

- PCI Interface

- ISA Interface

- · Reset Logic

- Keyboard Controller

- Power Management Logic

- · AT Refresh Logic

- Pre-Read/Post-Write Buffers

- BIOS ROM Control

- Timer/Counter Logic

- DMA Controllers

- Dual-Channel Enhanced IDE Controller

- · Real-Time-Clock with 32-kHz Oscillator

- Interrupt Controllers

- USB Host Controller

#### **PCI Bus Interface**

The CY82C693UB provides a bridge for transactions between the PCI bus, the ISA bus, and IDE peripherals. PCI bus speeds of 25, 30, or 33 MHz are supported. The PCI interface is master/slave (it can initiate or be a target for transactions). The PCI bus interface in the CY82C693UB is Revision 2.1 compliant. This standard allows for a multitude of high-speed peripheral

cards to be added to the system. PCI is the predominant local bus for Pentium systems.

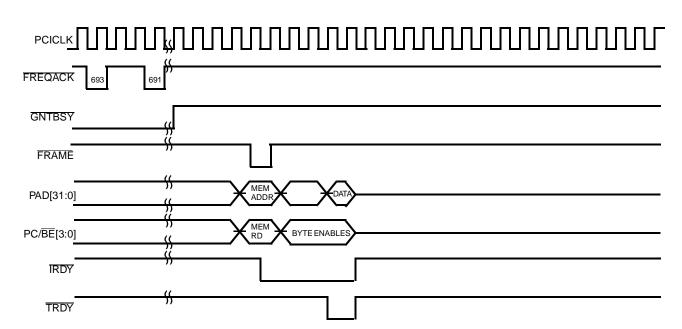

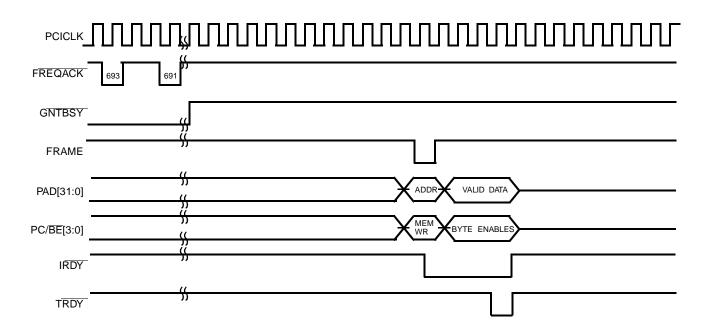

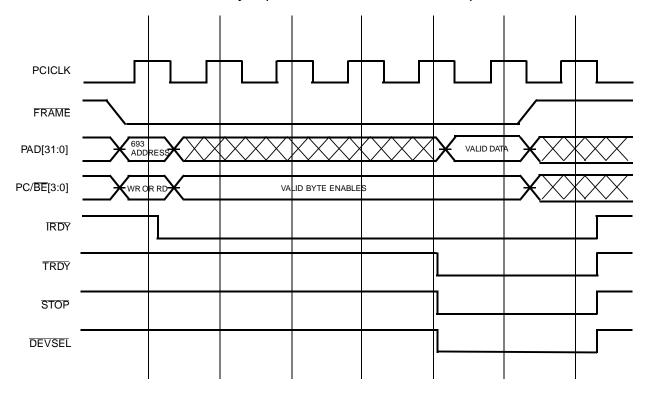

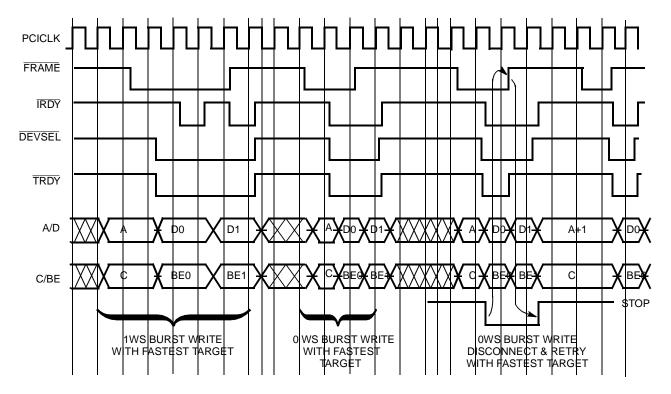

Master cycles are initiated by driving FRAME LOW with a valid address on AD[31:0], valid even address parity on PAR, and a valid command on C/BE[3:0]. Data phases occur when IRDY (initiator ready) and TRDY (target ready) are both active, valid data is placed on AD[31:0], the PAR signal is driven to reflect even parity, and the correct byte enable combination is present on C/BE[3:0]. Wait states can be inserted into a transaction if the initiator deasserts IRDY or the target deasserts TRDY. A transaction is terminated by the deassertion of FRAME prior to the final data phase. As a PCI master, the CY82C693UB will only perform memory read and write transactions. A read or write cycle consists of a maximum of 4 bytes of data in a single data cycle.

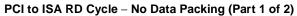

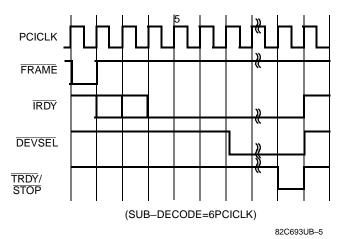

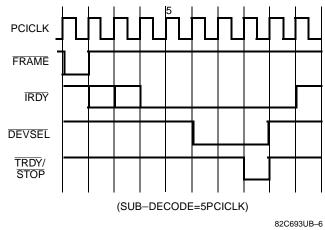

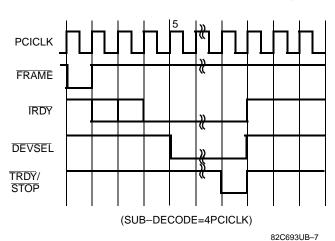

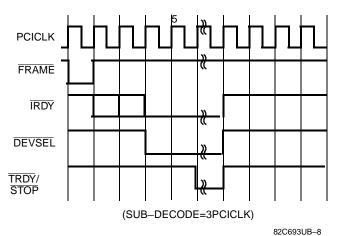

The CY82C693UB uses a subtractive decode strategy to determine if a PCI target transaction is destined for the ISA bus. Potential PCI targets decode any valid address during the first cycle of the transaction (FRAME asserted). If a PCI peripheral device (including the integrated IDE controller in the CY82C693UB) detects a transaction to its address space, it will assert DEVSEL. If the CY82C693UB does not detect the assertion of DEVSEL by another target (or its own IDE controller) within 4 PCI clock cycles, it will claim the transaction by asserting DEVSEL. All transactions that are not claimed by a PCI peripheral are, by default, sent to the ISA bus. After asserting DEVSEL, the CY82C693UB will initiate an ISA cycle and assert TRDY to the PCI bus when valid data is available.

As a PCI slave, the CY82C693UB will target-terminate the cycle after the first data transfer by asserting STOP with TRDY if FRAME is not deasserted before the data phase. The CY82C693UB does not accept bursts as a target. By not allowing target bursts, PCI bus bandwidth, which would otherwise be quickly consumed by ISA or IDE targets, is conserved.

The CY82C693UB supports PCI error reporting through the SERR (system error) signal. Both internally detected and externally generated errors are reported. SERR is asserted for any system error, including address/data parity errors on Special Cycle commands, except for data parity. If the CY82C693UB detects the assertion of SERR, it will assert NMI (non-maskable interrupt) to the CPU. The CY82C693UB will store the source of the NMI (SERR) in an internal configuration register to allow the NMI handler software to determine the cause of the error.

The CY82C693UB supports the four PCI interrupt signals (INTA, INTB, INTC, and INTD). The interrupt lines are open-drain and should be routed to all of the PCI slots. For single-function devices, only INTA should be used. The three other interrupt lines can be connected to any set of functions on a multi-function device. Each interrupt signal can be programmed to be level-sensitive (PCI Compliant) or edge-triggered (not PCI Compliant). The assertion of a PCI interrupt request will cause the INTR signal to be asserted to the processor. When the processor performs an interrupt acknowledge cycle, the CY82C693UB will return an interrupt vector based on the level of the PCI interrupt. The PCI interrupt levels are programmable. Interrupt programmability is useful in resolving system conflicts.

The CY82C693UB contains the PCI arbiter. The CY82C693UB supports up to five PCI masters, including the CY82C691. There are four dedicated request and grant line pairs, one for each slot, and a special busy and grant for the

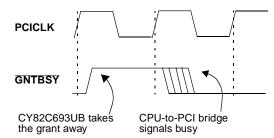

CY82C691. The CY82C691 is the default owner of the PCI bus. If the CY82C691 requires ownership of PCI and is granted the bus, it will assert the GNTBSY signal. When the CY82C693UB sees another master's request asserted, and no higher priority masters are requesting the bus, the CY82C693UB will remove the grant from the CY82C691 and give the grant to the new master. The CY82C693UB supports rotating priority. In rotating priority, the last master to be granted the bus becomes lowest priority. The CY82C691 is always given highest priority to reduce CPU latency due to arbitration.

#### ISA Bus Interface

The CY82C693UB contains an ISA (Industry Standard Architecture) Bus interface. If no other target in the system claims the transaction, it is passed to the ISA bus. The ISA bus interface in the CY82C693UB is full master/slave, allowing a myriad of low-cost peripheral cards to be added to the system.

ISA master cycles are performed by the CY82C693UB whenever a PCI master wants to access an ISA peripheral card. The CY82C693UB drives the address onto the ISA address lines and asserts BALE. The accessed resource will then respond with its size by the assertion/negation of the IOCS16 or MEMCS16 signals. The appropriate command signals (SMEMR, SMEMW, MEMR, MEMW, IOR, or IOW) will then be asserted by the CY82C693UB. The deassertion of the active command signal indicates when valid data is on the bus. Wait states can be inserted into an ISA cycle by the target's negation of the IOCHRDY signal. This forces the command signal to stay on the bus until IOCHRDY is asserted again.

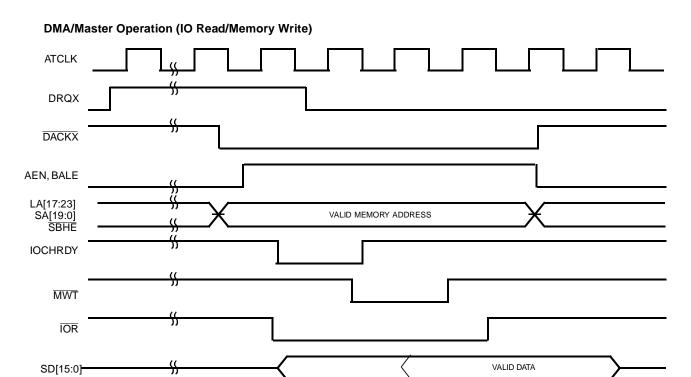

An ISA peripheral requests ownership of the ISA bus by asserting its DMA request signal. The request can be either a normal ISA transaction controlled by the peripheral itself, or a DMA transaction using transfer parameters (such as starting address and block count) previously set up in the DMA controller inside the CY82C693UB.

In a normal ISA transaction, the ISA master begins its transfers after receiving DMA acknowledge from the CY82C693UB. The CY82C693UB differentiates a normal ISA bus request from an ISA DMA request by checking the transfer parameters (in the on-chip DMA controller) corresponding to the above DMA request signal. If no transfer parameters are stored, then the request is a normal ISA transfer.

If the ISA request is a DMA transfer, the CY82C693UB outputs the pre-programmed starting address and the control signals onto the ISA bus. It will also assert AEN to the requesting ISA bus master so that it will ignore the address and simply provide the data to be transferred onto the ISA bus. The address on the ISA bus is the memory address used to route the DMA data to the proper memory location. If the target for a DMA/MASTER ISA cycle is on the PCI bus, the PCI bus will be arbitrated for before the CY82C693UB will assert the DMA acknowledge to the ISA master.

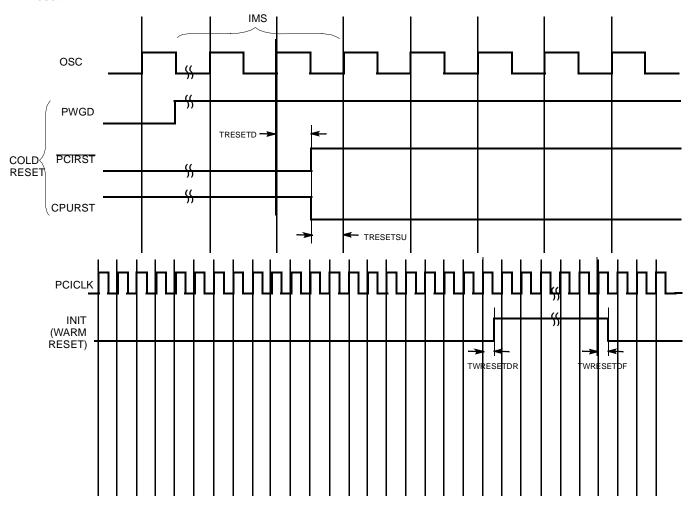

When either an ISA master request or a DMA request is asserted to the CY82C693UB, system data coherency must be maintained. This is accomplished using two sideband signals between the CY82C691 and the CY82C693UB (FREQACK and GNTBSY). When the CY82C693UB detects the assertion of one of the DMA request signals, it will assert FREQACK for one clock cycle. This is a request to the CY82C691 to flush all write buffers. After driving FREQACK for one cycle, the CY82C693UB will drive the signal deasserted (HIGH) for one PCI clock cycle and float the signal (rescind). After the

CY82C691 has flushed its write buffers (causing memory to be coherent with respect to the write buffer contents), the CY82C691 will assert FREQACK for one PCI clock cycle and rescind. This informs the CY82C693UB that the write buffers have been flushed and it is free to take control of the PCI bus and perform the ISA master/DMA transfer.

GNTBSY performs the PCI arbitration function between the CY82C691 and the CY82C693UB. The CY82C691 is the default owner of the PCI bus (GNTBSY is asserted LOW by the CY82C693UB in the default state). When the CY82C693UB wants access to the PCI bus, it drives GNTBSY HIGH for one PCI clock cycle and rescinds the signal. If the CY82C691 has a PCI bus cycle pending, it will drive GNTBSY LOW until it is finished with its transaction (PCI bus busy). Once the CY82C691 has finished its pending transaction, it will deassert GNTBSY and rescind. When the CY82C693UB sees GNTB-SY deasserted, it is free to grant the PCI bus to another master. The CY82C693UB will leave GNTBSY deasserted as long as a master other than the CY82C691 is on the PCI bus. Once the other PCI masters finish their transactions, the CY82C693UB will assert GNTBSY to inform the CY82C691 that it is free to take the PCI bus again.